lmxyy

1

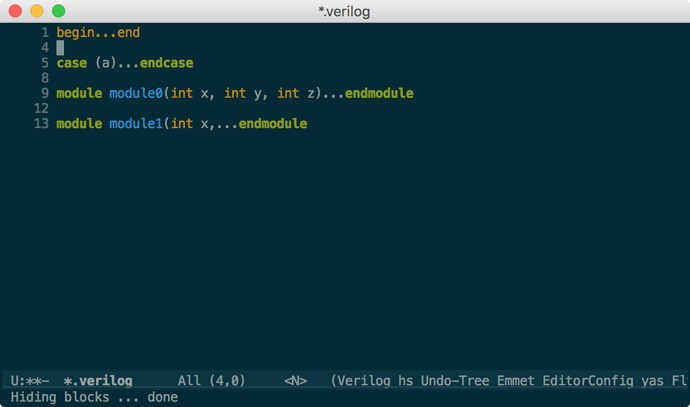

发现自己看完了HideShow后,还是不会自己定制verilog下的hide and show block.

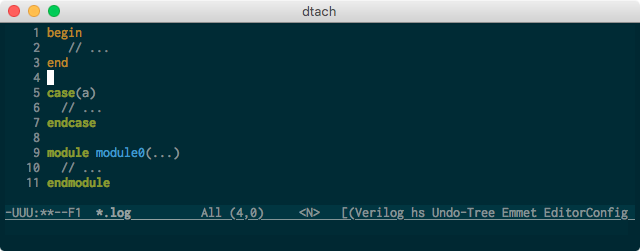

比如我要hide

begin

...

end

case(a)

...

endcase

module module0(...)

...

endmodule

这三个东西,用

(defvar hs-special-modes-alist

(mapcar 'purecopy

'(

(verilog-mode "begin" "end" "/[*/]" nil nil)

)

)

)

结果并hide不了begin ... end。

有人能够解释下上面语句是干这个的吗?要hide上面的代码块,elisp应该怎么写啊?

- 写法不对

hs-special-modes-alist 是 HideShow 的变量,如果你先定义了,那么 HideShow 的定义无效;如果 HideShow 先加载,你的定义无效。

- 用法不对

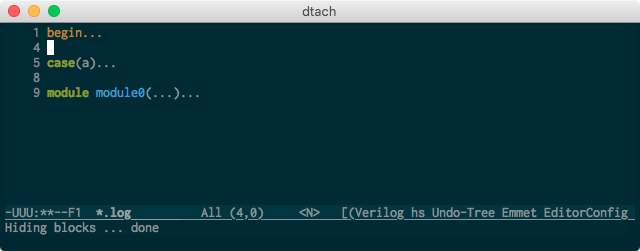

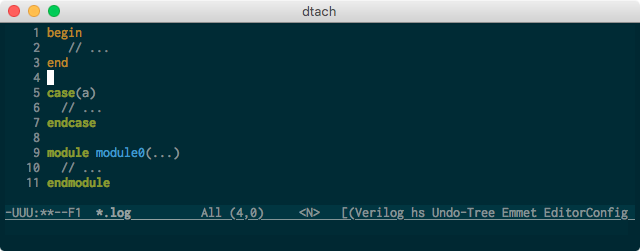

Verilog 其实已经向 hs-special-modes-alist 添加了规则,begin...end 是可以折叠的,但是光标位置要在 begin 的 b 字母 或 end 任意字母上,或者光标在 begin...end 之外

- 添加对

case/module 的支持:

(setq hs-special-modes-alist

(cons '(verilog-mode "\\<\\(begin\\|case\\|module\\)\\>"

"\\<\\(end\\|endcase\\|endmodule\\))\\>"

nil verilog-forward-sexp-function)

hs-special-modes-alist))

lmxyy

3

您好,我使用了您

(setq hs-special-modes-alist

(cons '(verilog-mode "\\<\\(begin\\|case\\|module\\)\\>"

"\\<\\(end\\|endcase\\|endmodule\\))\\>"

nil verilog-forward-sexp-function)

hs-special-modes-alist))

这段代码,发现了一个问题:

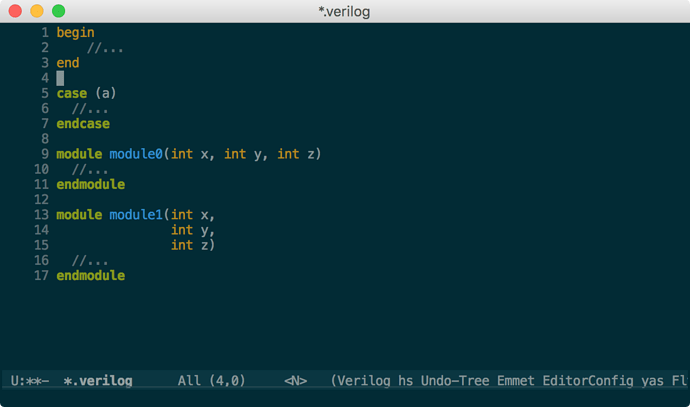

如果我代码这样写,他可以正常Hide:

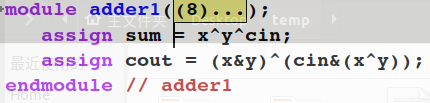

module adder1(x,y,sum,cin,cout);

input x,y,cin;

output sum,cout;

assign sum = x^y^cin;

assign cout = (x&y)^(cin&(x^y));

endmodule // adder1

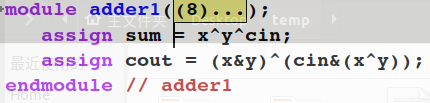

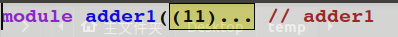

但是,如果我这样写,他的Hide起来就有点诡异了:

但是,如果我这样写,他的Hide起来就有点诡异了:

module adder1(

input x,

input y,

input cin,

output sum,

output cout

);

assign sum = x^y^cin;

assign cout = (x&y)^(cin&(x^y));

endmodule // adder1

多出来了一个莫名其妙的括号。。。

在不加您的代码之前,我记得我是可以对module括号后内容进行hide的,但是加了代码后好像不行了。。。

就像这样

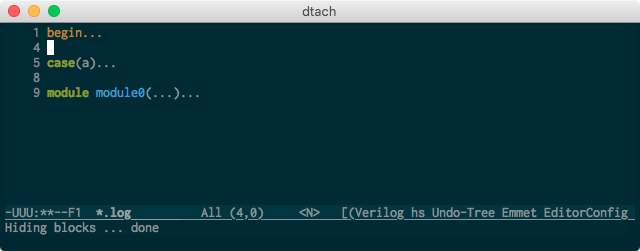

而且感觉

begin

...

end

hide之后留下了个

begin

...

感觉有点奇怪。。。

lmxyy

5

我的意思是,begin ... end折叠后,还剩下一个begin很奇怪。

因为在c++中,如果你折叠

if (a == b)

{

a++;

b++;

}

肯定应该是

if (a == b) {...}

不会是

if (a == b}

{...

这个样子,就是begin end充当大括号的作用,hide之后还剩下一个begin就相当于剩下一个左大括号,就有点奇怪,不是指省略号奇怪。。。

表达出现了偏差,抱歉。。。

改成:

"\\(\\<begin\\>\\|\\<case\\>\\|\\<module\\>\\)"

"\\(\\<end\\>\\|\\<endcase\\>\\|\\<endmodule\\>\\)"

如果需要更精确的匹配,参考 verilog-forward-sexp 函数。

你的例子当中:

if (a == b)

{

a++;

b++;

}

折叠之后应该是:

if (a == b)

{...}

不应该是 if (a == b) {...}