RT, 写Verilog的时候要写类似于下面这种重复的代码段(其实就是生成一些重复的硬件)。是否有能够方便在Emacs内地生成这种格式化的代码的方法(也许类似于正则表达式)。现在的方案是使用Mathematica生成后复制过来,但是和Emacs契合度不够。

case(write_ptr)

5'd0 : memory[0] <= data_w;

5'd1 : memory[1] <= data_w;

5'd2 : memory[2] <= data_w;

5'd3 : memory[3] <= data_w;

5'd4 : memory[4] <= data_w;

5'd5 : memory[5] <= data_w;

5'd6 : memory[6] <= data_w;

5'd7 : memory[7] <= data_w;

5'd8 : memory[8] <= data_w;

5'd9 : memory[9] <= data_w;

5'd10 : memory[10] <= data_w;

5'd11 : memory[11] <= data_w;

5'd12 : memory[12] <= data_w;

5'd13 : memory[13] <= data_w;

5'd14 : memory[14] <= data_w;

5'd15 : memory[15] <= data_w;

5'd16 : memory[16] <= data_w;

好像道友中写Verilog的不是很多。这个的主要需求是用在case语句中给一片连续内存单元赋值,需要能够做到生成从0~n的格式化代码,n同时最好能有各种进制转换及用0补齐到k位(主要是2进制和16进制转换,同时保证位对齐)。例如希望的效果是

5'b00000 : memory[0] <= data_w; //输入第一行

xxxxx操作后:

5'b00000 : memory[0] <= data_w;

5'b00001 : memory[1] <= data_w;

5'b00010 : memory[2] <= data_w;

5'b00011 : memory[3] <= data_w;

5'b00100 : memory[4] <= data_w;

5'b00101 : memory[5] <= data_w;

5'b00110 : memory[6] <= data_w;

......

5'b01000 : memory[16] <= data_w;

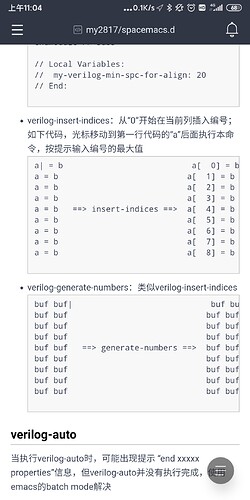

通过宏录制/verilog生成索引号/tiny可以很好地生成索引。假如能有类似于正则表达式这种更加完备且简约的生成方式就更赞了(其实是录制宏经常会误操作)。