有使用emacs来写verilog/systemverilog的吗? 进来一起交流下~

来了,好像针对硬件开发的完整环境配置较少(比如集成的verilog-snippet 等 )

我之前用vim,后来感觉emacs功能更强大点,最近上手感觉没法真正用起来,更多的还是当一个原始编辑器再用,希望能跟你们学习下~PS:我主要在windows下,虚拟机跑了一个ubuntu,不过也是刚开始

我一直没把sv 的lsp用起来,现在用的citre 没法精准跳转和查引用,写代码还是差点意思

还在摸索使用emacs verilog mode的auto用法。。

sv的lsp我都试了一遍,的确一个能用的都没,我混合citre和tabnine一起用了一段时间,最后索性都关了,直接用consult搜索,hide show折叠代码,consult-imenu 大范围跳转,习惯了也还好😄

我是小白,请问citre该怎么配置呀,可否分享下配置呢

我用hide show 抄子坛友的配置把 hs-special-modes-alist 中的verilog-mode 相关的配成了 (verilog-mode “\<begin\>\|\<task\>\|\<function\>\|\<class\>\|\<module\>\|\<package\>\|(” “\<end\>\|\<endtask\>\|\<endfunction\>\|\<endclass\>\|\<endmodule\>\|\<endpackage\>\|)” nil verilog-forward-sexp-function) 发现在某些 如果在一个package 里面执行+fold/close-all 会把整个package 折叠起来, 其实我只是想把task function begin 这些块折叠, 于是我把 hs-special-modes-alist 配成了 (verilog-mode “\<begin\>\|\<task\>\|\<function\>\|(” “\<end\>\|\<endtask\>\|\<endfunction\>\|)” nil verilog-forward-sexp-function) 发现在含有package class 的文件中执行 +fold/close-all 会卡死, 如果把 hs-special-modes-alist 中的括号配置项去掉就不会, 不知道你遇到过这种情况没有? 不加括号又折叠不了实例, 我现在的做法是 advice +fold/close-all 在执行这个函数前去根据光标上下两行的内容来动态的改变hs-special-modes-alist 但是这种办法还是不完美

(require 'citre-config)

(setq citre-use-project-root-when-creating-tags t

citre-prompt-language-for-ctags-command t

citre-auto-enable-citre-mode-modes '(prog-mode)

)

citre 不需要特殊配置, 这样就行, 然后把这些function 找个键位绑定

'("e c a" . citre-ace-peek)

'(citre-jump)

'(citre-peek)

'(citre-jump-back)

'(citre-update-this-tags-file)

'(citre-peek-restore)

'(citre-peek-save-session)

'(citre-peek-load-session)

你试试这样. 其他的关键词也是类似的写发就行. 能折叠各种 block , 也可以嵌套折叠

(add-to-list 'hs-special-modes-alist '(verilog-mode "\\(\\<begin\\>\\|\\<case\\>\\|\\<module\\>\\|\\<class\\>\\|\\<function\\>\\|\\<task\\>\\)"

"\\(\\<end\\>\\|\\<endcase\\>\\|\\<endmodule\\>\\|\\<endclass\\>\\|\\<endfunction\\>\\|\\<endtask\\>\\)" nil verilog-forward-sexp-function))

如果你是evil 用户的话, 可以用这样类似的键位

'("z a" . hs-toggle-hiding) ;; toggle block

'("z c" . hs-hide-block)

'("z o" . hs-show-block)

'("z m" . hs-hide-all) ;; hide all blocks in current buffer

'("z r" . hs-show-all) ;; expand all blocks in current buffer

折叠的我也能用,我碰到的问题是在有package class 的文件中,折叠关键字不包含package 和 module 和 class 的时候,按zm全部折叠就会卡死,原因就是折叠关键字中包含了括号,把括号去掉即不折叠实例就不会卡死

有杨例代码吗,我调试一下试试

citre 配置可以参考这篇, https://skfwe.cn/post/citre_verilog/ 里面把你的ctags 这些可执行文件改成你自己的,再把里面一堆你没有对应函数的按键绑定的删掉就行了, 配置里简单hack了一下citre 的jump函数,使得跳转后光标定位到关键词上

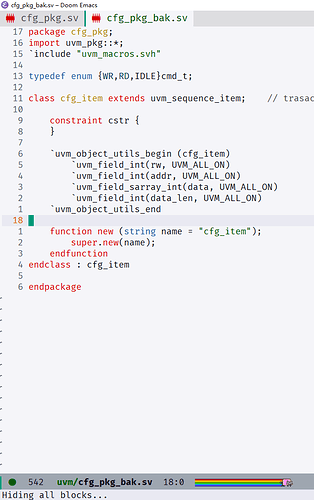

package cfg_pkg;

import uvm_pkg::*;

`include "uvm_macros.svh"

typedef enum {WR,RD,IDLE}cmd_t;

class cfg_item extends uvm_sequence_item; // trasaction

constraint cstr {

}

`uvm_object_utils_begin (cfg_item)

`uvm_field_int(rw, UVM_ALL_ON)

`uvm_field_int(addr, UVM_ALL_ON)

`uvm_field_sarray_int(data, UVM_ALL_ON)

`uvm_field_int(data_len, UVM_ALL_ON)

`uvm_object_utils_end

function new (string name = "cfg_item");

super.new(name);

endfunction

endclass : cfg_item

endpackage

zm 之后会卡死

hs-special-modes-alist 使用如下配置

(map-put hs-special-modes-alist 'verilog-mode '("\\<begin\\>\\|\\<task\\>\\|\\<function\\>\\|(" "\\<end\\>\\|\\<endtask\\>\\|\\<endfunction\\>\\|)" nil verilog-forward-sexp-function))

问题出在

`uvm_object_utils_begin (cfg_item)

这一句, 把这句注释掉就可以正常折叠了。。。

我用了 hide-all, 很流畅…

你的配置不是我的配置呀 你的都把class折叠了, 你的配置里面肯定没有 “(” “)” 这一对

哦哦, 我用的我自己的配置, 没细看. 这个() 是用来折叠实例名或参数么

对比了一下你的代码和我的, 我没把握到你这样的目的, 不好意思爱莫能助了

是的 , 类似这种

demo dut (

.abc(abc),

.abc(abc),

.abc(abc)

) ;

、...(...) 这种就会导致折叠失败, 把、删掉就行了, 我现在的做法是 zm 之前检查buffer 如果存在可能导致折叠失败的文本则把括号去掉, 否则就保留折叠实例的功能

嗯嗯,原来如此,hide我不怎么懂,等一个大佬来看看

好的, 没事, 代码折叠我其实用得不多,现在这样也够用了